제 26회 반도체 대전 SEDEX 2024

October 23 ~ 25 / COEX SEOUL

2024 참가업체 디렉토리

(주)잇다반도체

ITDA SEMICONDUCTOR CO,. LTD.

Booth No.C309- CEO전호연 / Ho Yeon Jeon

- ADDRESS경기도 화성시 동탄역로 150, 지하 3층 103호 (오산동, 동탄역 롯데캐슬) / 160, Dongtanyeok-ro, Hwaseong-si, Gyeonggi-do, Republic of Korea (18478)

- CONTACTTel. 82-70-5001-0706 / Fax. 82- / URL. https://itdasemi.com

-

제조품목

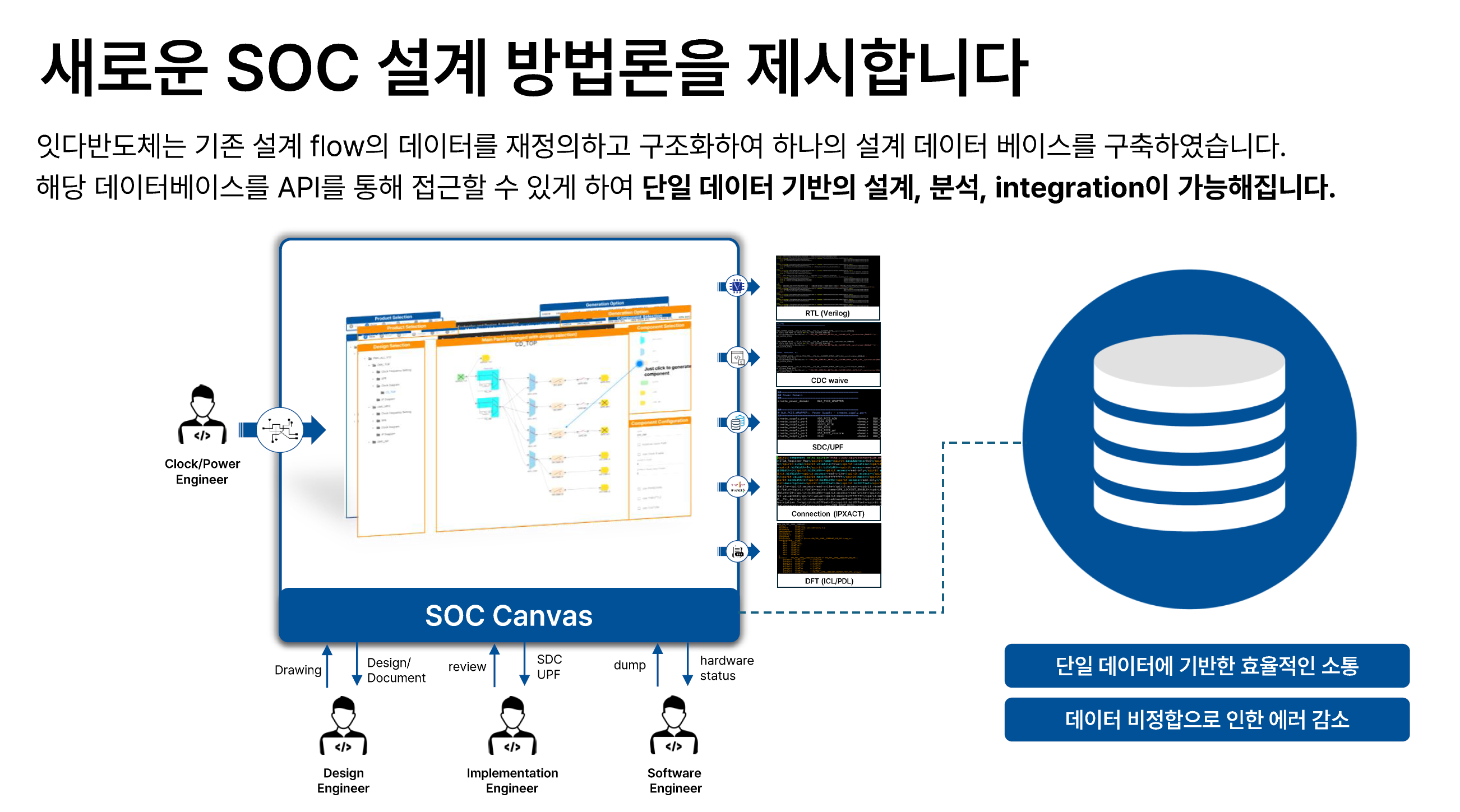

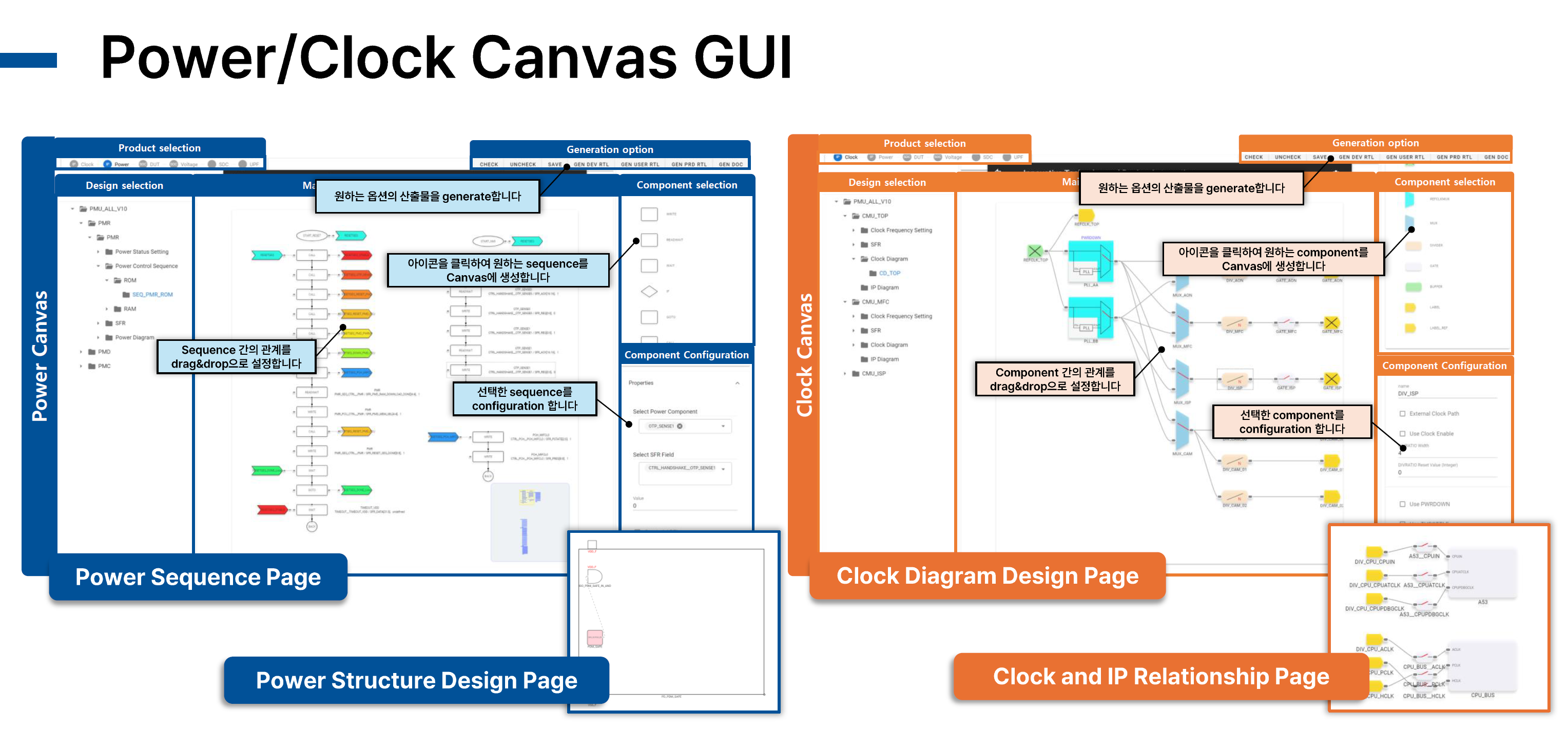

SOC Canvas는 SOC(System On Chip)의 power와 clock 시스템을 하드웨어 레벨에서 GUI(Graphical User Interface)를 통해 설계할 수 있게 하는 시스템 IP 개념의 제품입니다.

SOC Canvas에서는 GUI를 통해 추상적인 하드웨어 모델만 설계하면, 제품 내 미리 구성되어 있는 하드웨어 모델과 소프트웨어 framework를 통해 자동으로 산출물을 생성하여 기존에 매우 복잡했던 power/clock system design flow를 단순화시켰습니다. power/clock system 컴포넌트들을 정형화시키고, 이를 소프트웨어로 구조화하여 기존 몇천, 몇만 줄 단위의 복잡한 RTL 코드를 추상화된 웹기반 GUI로 디자인할 수 있게 됩니다. GUI로 설계된 디자인을 통해 Verilog, SDC 등의 산출물을 생성하는 데에는 10분이 채 소요되지 않습니다.

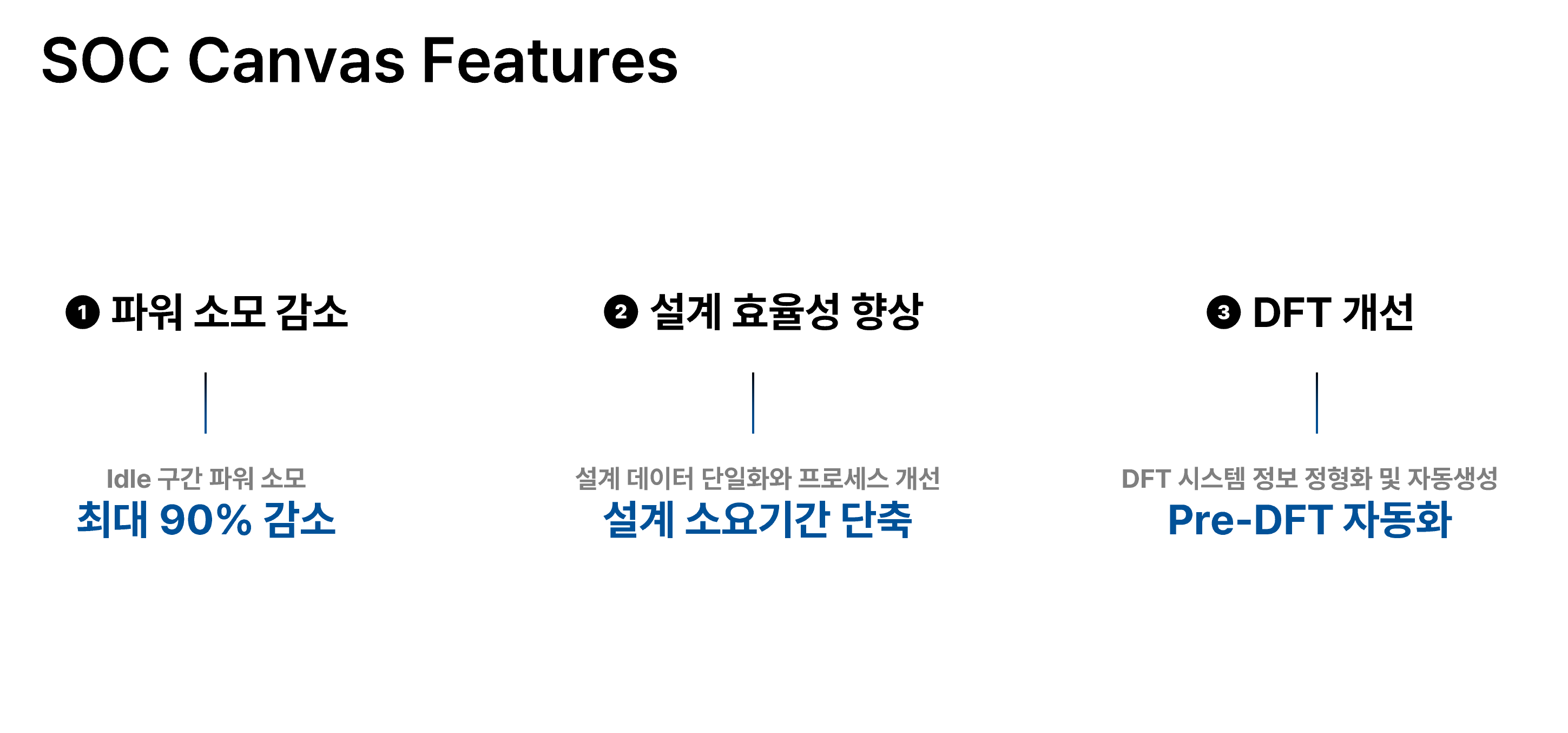

SOC Canvas의 power/clock controller는 개별 도메인을 하드웨어 레벨에서 power gating을 통해 제어하기 때문에 idle 구간에서의 파워 소모을 80~90%까지 낮출 수 있습니다. 또한 도메인 별 제어 방식을 정형화하여 하드웨어 embedded software 복잡도 또한 낮아집니다. power/clock 컨트롤러를 정형화시켜 큰 칩도 쉽계 설계 가능하며, power controller 내 sequence를 바이너리로 구성하여 파워 에러를 쉽게 수정할 수 있습니다.

SOC Canvas is a system IP product that enables the design of SOC (System On Chip) power and clock systems at the hardware level through a GUI (Graphical User Interface).With SOC Canvas, you can design abstract hardware models through the GUI. The product automatically generates outputs using pre-configured hardware models and software frameworks, simplifying the traditionally complex power/clock system design flow. By standardizing power/clock system components and structuring them in software, SOC Canvas allows the design of complex RTL code, often spanning thousands or tens of thousands of lines, through an abstract web-based GUI. Generating outputs like Verilog and SDC from GUI-designed models takes less than 10 minutes.The power/clock controller in SOC Canvas controls individual domains at the hardware level through power gating, reducing power consumption during idle periods by up to 80-90%. Additionally, by standardizing domain-specific control methods, the complexity of embedded software for hardware is also reduced. The standardized power/clock controller simplifies the design of large chips, and sequencing within the power controller can be configured in binary format for easy error correction.

-

회사소개

반도체 시스템 설계는 왜 어려울까요?

고성능, 저전력 칩을 양산하기 위해서는 정교하고 최적화된 시스템 설계가 필수적입니다. 하지만 칩의 Power, Clock 도메인을 최적화해서 설계하기 위해서는 성공적인 프로젝트 경험을 가진 전문 엔지니어가 필요합니다. 또한, 시장에서의 칩 요구 성능과 다양성이 높아짐에 따라 칩 시스템 설계의 난이도와 비용도 기하급수적으로 커지고 있습니다.

잇다반도체는 16년 이상의 power, clock, DFT 시스템 설계 경험을 통해 칩 시스템 설계 비용, time to market, 리스크를 줄일 수 있는 파트너가 될 것을 약속 드립니다.

잇다반도체는 2022년 9월에 문을 연 이래 딥테크 팁스 프로그램, 초격차 스타트업에 선정되는 등 기술적 역량을 인정받아 빠르게 성장하고 있습니다. 24년 4월에는 시리즈 A 투자를 유치하였으며, 현재 국내외 주요 반도체 팹리스와 협업 논의 중에 있습니다.

Why is semiconductor system design difficult?

To mass-produce high-performance, low-power chips, precise and optimized system design is essential. However, optimizing a chip's power and clock domains requires specialized engineers with successful project experience. Additionally, as the market demands higher performance and diversity in chips, the complexity and cost of chip system design are increasing exponentially.

ITDA Semiconductor promises to be your partner in reducing chip system design costs, time to market, and risks through over 16 years of experience in power, clock, and DFT system design.

Since its inception in September 2022, ITDA Semiconductor has been rapidly growing, recognized for its technical prowess by being selected for programs like the Deep Tech TIPS. In April 2024, we secured Series A funding and are currently in discussions with major domestic and international semiconductor fabless companies.

-

온라인 상담스케쥴

반도체대전에 대한 안내 날짜/시간 10:00 11:00 12:00 13:00 14:00 15:00 16:00 10월 23일 10월 24일 10월 25일